University of Oslo Department of Informatics

Offloading Multimedia Proxies using Network Processors

Cand. Scient thesis Øyvind Hvamstad

Published August 2004

#### **Offloading Multimedia Proxies using Network Processors**

Øyvind Hvamstad

Published August 2004

#### Abstract

A Multimedia Proxy aims to reduce the client startup latency, network load and server load. Such a proxy may be subject to many concurrent clients and experience high processing loads due to for example transcoding or protocol translation. At the same time a high load can be experienced when fetching data from the server. In this thesis, we will explore how to offload a multimedia streaming proxy by using network processing technology. We design, implement and evaluate a proxy prototype on the IXP1200 network processor. As a proof-of-concept we show that the prototype successfully offloads the proxy host in the data-plane, i.e., no data packets are processed by the host CPU, leaving it free to perform other CPU intensitive tasks. The prototype is able to do application layer forwarding using approximately a thenth of the cycles compared to a traditional architecture, where all pakcets are processed by the host CPU.

## **Table of Contents**

|              | Introduction                              |      |

|--------------|-------------------------------------------|------|

|              | 1.1. Motivation and background            | 1    |

|              | 1.2. Problem definition                   | 2    |

|              | 1.3. Outline of document                  | 3    |

| <b>I</b> . ] | Background                                | 5    |

|              | 2. Distributed multimedia systems         | 7    |

|              | 2.1. General                              | 7    |

|              | 2.1.1. Classification                     | 7    |

|              | 2.1.1.1. Taxonomy of applications         | 7    |

|              | 2.1.1.2. Synchronicity                    | 8    |

|              | 2.1.1.3. Interaction                      |      |

|              | 2.1.1.4. Classifying MoD                  | 9    |

|              | 2.2. Requirements                         | 9    |

|              | 2.3. MoD access patterns                  |      |

|              | 2.4. Distribution architectures           | .11  |

|              | 2.5. Protocol overview                    | .13  |

|              | 2.5.1. Real Time Streaming Protocol       | .13  |

|              | 2.5.2. Real-Time Transport Protocol       |      |

|              | 2.5.3. Session Description Protocol       |      |

|              | 2.6. Summary & challenges                 |      |

|              | 3. Proxies                                |      |

|              | 3.1. General                              | . 17 |

|              | 3.2. MoD proxy caches                     |      |

|              | 3.2.1. Properties                         |      |

|              | 3.2.2. Caching strategies                 |      |

|              | 3.3. Cache architectures                  |      |

|              | 3.4. Data flow                            |      |

|              | 3.4.1. Copy operations                    |      |

|              | 3.4.2. The Linux network stack            |      |

|              | 3.5. Summary                              | .25  |

|              | 4. Network processors                     |      |

|              | 4.1. General                              |      |

|              | 4.1.1. NIC evolution                      |      |

|              | 4.2. Intel Internet Exchange Architecture |      |

|              | 4.3. Intel IXP1200 network processor      |      |

|              | 4.3.1. The StrongARM core CPU             |      |

|              | 4.3.2. Microengines                       | .33  |

|              | 4.3.3. The FBI unit                       |      |

|              | 4.3.4. Memory interfaces                  |      |

|              | 4.4. IXA application development          |      |

|              | 4.5. ACE run-time framework               |      |

|              | 4.6. Related work                         |      |

|              | 4.6.1. Network layer                      |      |

|              | 4.6.2. Multimedia streaming               |      |

|              | 4.7. Summary                              |      |

| II.          | Design, implementation and evaluation     |      |

|              | 5. Design and implementation              |      |

|              | 5.1. Design                               |      |

|              | 5.1.1. Design goals                       |      |

|              | 5.1.2. Component overview                 |      |

|              | 5.1.3. Caching                            |      |

|              | 5.1.4. Fast forwarding                    |      |

|              | 5.1.5. Summary                            |      |

|              | J                                         | -    |

| 5.2. Implementation                  | 47 |

|--------------------------------------|----|

| 5.2.1. Limitations and assumptions   | 47 |

| 5.2.2. Overview                      | 48 |

| 5.2.3. The RTSP components           | 49 |

| 5.2.3.1. Conformance issues          | 51 |

| 5.2.4. Session management            | 52 |

| 5.2.5. Cache management              |    |

| 5.2.6. Packet classification         | 53 |

| 5.2.6.1. Classification rules        | 53 |

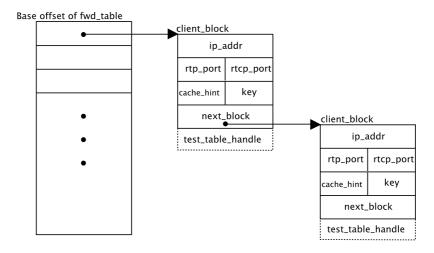

| 5.2.6.2. Forwarding table            | 55 |

| 5.2.7. RTP forwarding                | 58 |

| 5.2.8. Summary                       | 59 |

| 6. Experiments, results and analysis | 61 |

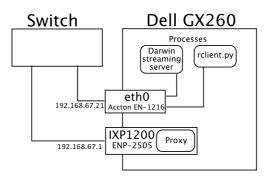

| 6.1. Testing environment             |    |

| 6.2. Measurements                    |    |

| 6.3. Results                         |    |

| 6.3.1. Packet types                  |    |

| 6.3.2. Ingress to egress             |    |

| 6.3.3. Deviation                     |    |

| 6.3.4. Processing overhead           |    |

| 6.3.5. Summary of results            |    |

| 6.4. The offloading effect           |    |

| 6.5. Prototype performance           |    |

| 6.6. Extensions                      |    |

| 6.6.1. Caching                       |    |

| 6.6.2. Zero-copy                     |    |

| 6.7. Summary                         |    |

| 7. Conclusions and future work       |    |

| 7.1. Conclusions                     |    |

| 7.2. Future work                     |    |

| References                           |    |

| A. Guide to the attached CD          |    |

| A.1. Directory structure             |    |

| A.2. Building the source             |    |

| A.3. Running the executables         | 83 |

|                                      |    |

## **List of Figures**

| 2.1. Taxonomy of applications                                                  | 8  |

|--------------------------------------------------------------------------------|----|

| 2.2. Distribution architectures                                                | 12 |

| 2.3. The OSI stack and the Internet protocol stack                             | 13 |

| 3.1. Basic proxy architecture                                                  | 17 |

| 3.2. Cache architecture                                                        |    |

| 3.3. Proxy data flow                                                           | 23 |

| 3.4. Proxy data-path                                                           | 24 |

| 3.5. Linux 2.0.34 network stack                                                | 25 |

| 4.1. Cost vs. performance                                                      |    |

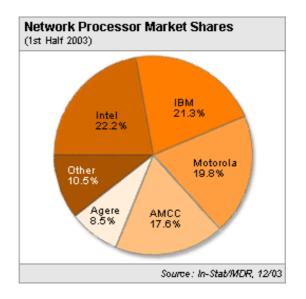

| 4.2. NPU market shares                                                         |    |

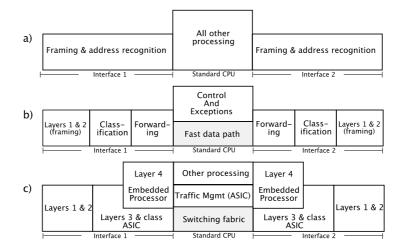

| 4.3. Three generations of NICs                                                 |    |

| 4.4. The Internet Exchange Architecture                                        |    |

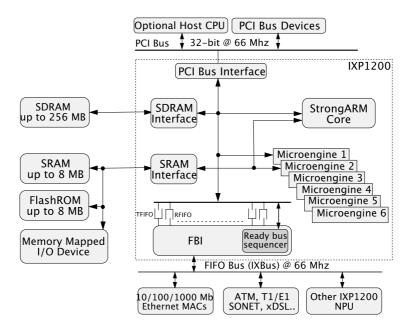

| 4.5. IXP1200 block diagram                                                     |    |

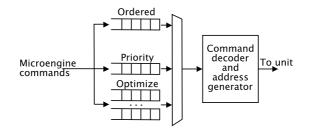

| 4.6. Command queues                                                            |    |

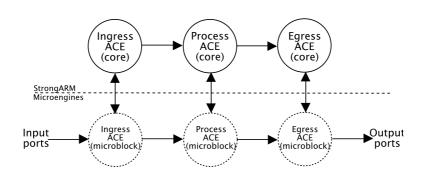

| 4.7. ACE processing pipeline                                                   |    |

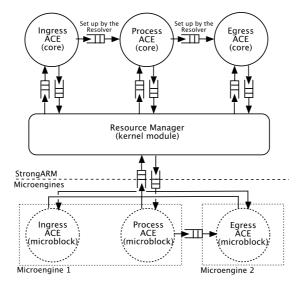

| 4.8. Core and microblock components of an ACE processing pipeline              |    |

| 4.9. ACE intercommunication                                                    | 40 |

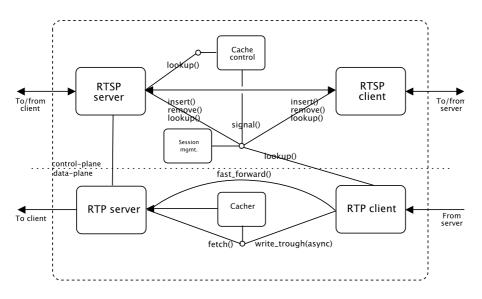

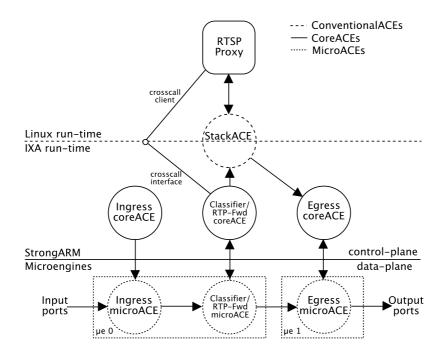

| 5.1. Proxy components                                                          | 46 |

| 5.2. ACE layout                                                                |    |

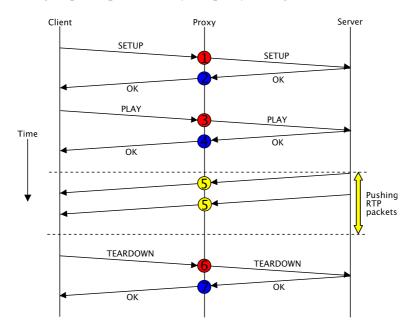

| 5.3. RTSP proxy session                                                        | 50 |

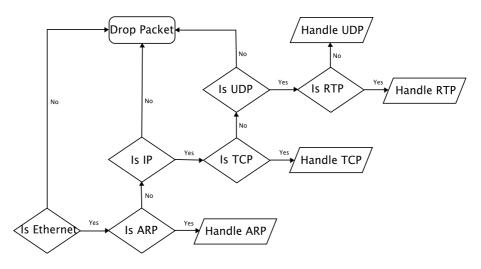

| 5.4. Packet classification                                                     | 53 |

| 5.5. Media Transport Forwarding table                                          | 57 |

| 6.1. Test configuration                                                        | 61 |

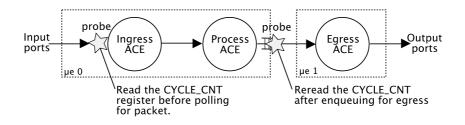

| 6.2. Experiment 1: Cycle probes for packet reception, forwarding and enqueuing |    |

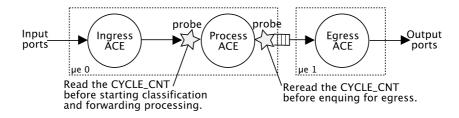

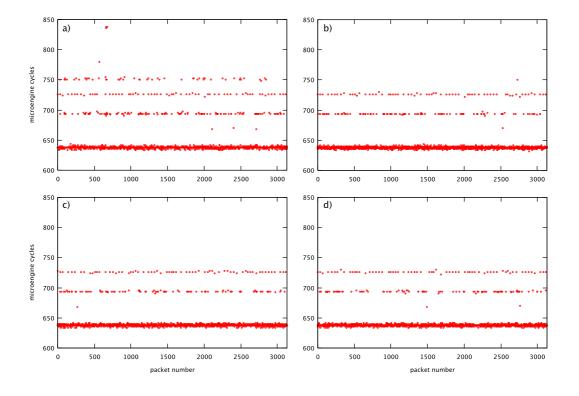

| 6.3. Experiment 2: Cycle probes for packet forward processing                  |    |

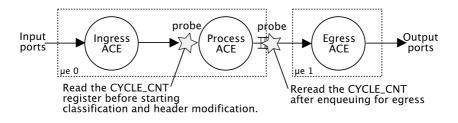

| 6.4. Experiment 3: Cycle probe for packet forward processing and enqueuing     |    |

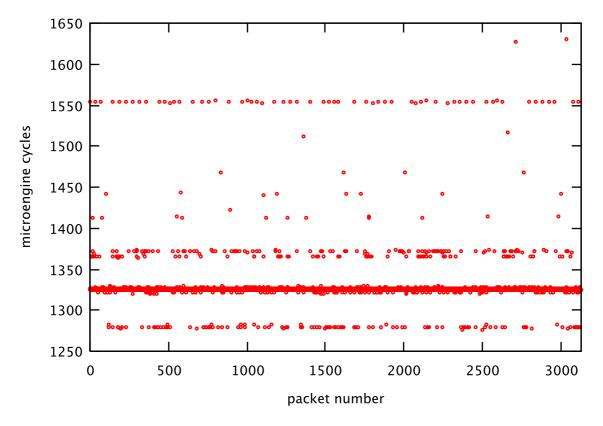

| 6.5. Cycles counted during packet reception, forwarding and enqueuing          |    |

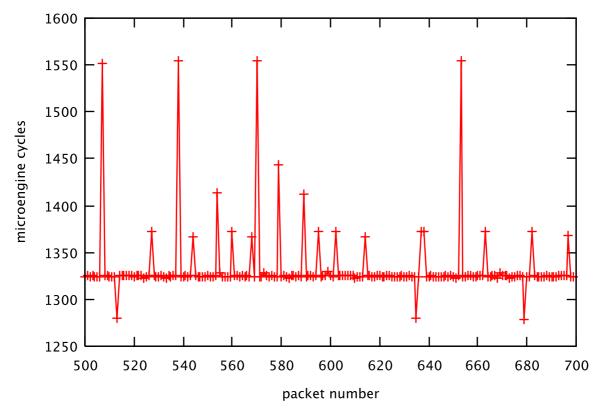

| 6.6. Packets 500 through 700 experiment 1                                      |    |

| 6.7. Cycles counted during packet forwarding                                   |    |

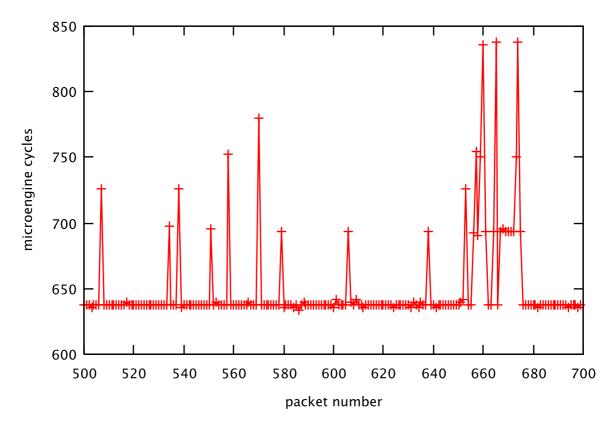

| 6.8. Packets 500 through 700 from experiment 2a)                               | 67 |

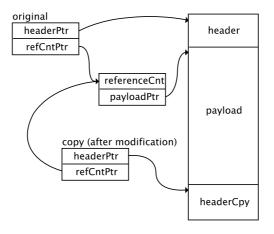

| 6.9. Lazy copy data-structure                                                  | 74 |

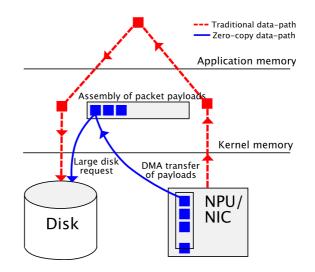

| 6.10. Zero copy data-path vs. traditional data-path                            | 75 |

### List of Tables

| 4.1. Processor hierarchy          | 29 |

|-----------------------------------|----|

| 4.2. IXP1200 memory interfaces    |    |

| 6.1. Packet count during session  |    |

| 6.2. Ingress to egress statistics |    |

| 6.3. Forwarding statistics        | 68 |

| 6.4. Experienced overhead         |    |

## List of Examples

| 2.1. Audio data rate and disk usage                              | 9  |

|------------------------------------------------------------------|----|

| 2.2. DVD data rate and disk usage                                | 10 |

| 2.3. DivX data rate and disk usage                               | 10 |

| 2.4. Basic RTSP session                                          | 14 |

| 5.1. RTSP request type                                           | 49 |

| 5.2. RTSP response type                                          | 50 |

| 5.3. Session object                                              | 52 |

| 5.4. Proxy session object                                        |    |

| 5.5. Simple branch classification of Ethernet type               |    |

| 5.6. IP address validation and transport protocol classification | 55 |

| 5.7. Hash function                                               |    |

| 5.8. Incremental checksumming                                    | 58 |

| 6.1. Microblock probes                                           | 62 |

| 6.2. Pseudo code for packet copy                                 |    |

### Chapter 1.

# Introduction

## 1.1. Motivation and background

People are always blaming circumstances for what they are. I don't believe in circumstances. The people who get on in this world are the people who get up and look for the circumstances they want and if they can't find them, make them.

—George Bernard Shaw

The Internet is growing at an exponential rate. The increasing availability of low-cost bandwidth for regular users enables new applications that have different requirements than the traditional applications. Streaming audio and video, Voice over IP (VoIP), Peer-to-Peer (P2P) networking, and Virtual Private Networks (VPNs) require more bandwidth and computation power than the retrieval of textual data. The ability to download audio and video content is quite common today. However, continuous playback of high-quality video often involves downloading large parts of or the whole object before viewing it. Streaming is to some extent possible, but usually the quality of such streams is low. Increased quality will be available as the bandwidth capabilities evolve in the Internet.

Nevertheless, large-scale deployment of *Media-on-Demand* (MoD) streaming applications in the Internet will introduce challenges. The philosophy on which the *Internet Protocol* (IP) is built, is loose coupling between heterogeneous networks along with end-to-end responsibility [Clark88]. These basic properties complicate the process of exercising *Quality Of Service* (QOS). Most, if not all, of the schemes proposed to guarantee some level of QOS are facing problems with scalability, fulfilling the actual level of guarantee or failing to achieve linear deployability [Xiao99].

The lack of a widely spread framework for handling resource reservation restrains the deployability of MoD. Such applications may require soft real-time guarantees, but will have to run on IP shared mediums without such support. Network effects such as latency and jitter along with possible congestion, contention and physical failures, will therefore reduce the perceived quality of the media and the system in general.

To circumvent the lack of QOS support in the Internet, pragmatic methods are used. Over-provisioning is commonly used by *Internet Service Providers* (ISPs). This basically means that extra resources are put into the network, enabling it to scale. For example, if the network load exceeds a certain percentage, the links are upgraded so that the level of redundant bandwidth is preserved. Further, if a server is experiencing high loads it is common to upgrade it with better hardware, or to put it in a load-balancing cluster, so that it may continue scaling to the number of concurrent clients.

Another pragmatic method is to reduce the resources needed to serve a client. This may involve reviewing and optimizing application protocols, improving the performance of servers [Halvorsen01], or the invention of new technologies that allow resources to be used differently. These efforts are less common. However, they are necessary, since over-provisioning cannot solve all problems related to scalability. Also, using over-provisioning as an indefinite measure might prove impractical and expensive.

A third way is to distribute the server tasks to an infrastructure of proxies. This has been discussed as a schema to help realize MoD in the Internet. Using proxies is also suggested in distributed gaming research. The proxies perform tasks on behalf of the server, e.g., by caching relevant data, shaping and adapting network traffic, etc. Serving clients from the proxy instead of directing them all the way to the server, reduces network load and latency.

A proxy cache, which sits somewhere between the server and the client, may experience a considerable amount of network traffic on both its up and down link. The proxy is therefore subject to the same challenges as the server. It is crucial that the proxy is able to efficiently process information without further adding to the delay. The faster a proxy can process a packet, the better throughput it will achieve. High throughput will allow the proxy to scale to a potentially high number of concurrent clients.

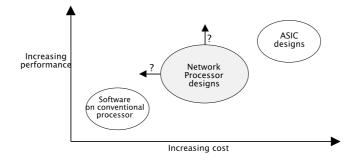

During the last years, a new generation of *Network Interface Cards* (NICs) has evolved. These have onboard *Network Processing Units* (NPUs), with programmable processing power and hardware specialized for network processing. The aim of NPUs is to provide flexibility and speed so that future and present challenges in network development can be met.

This thesis will investigate possible solutions to application specific challenges regarding multimedia proxy nodes by using an NPU, the IXP1200. We will focus on how to offload the proxy and achieving good throughput.

# **1.2. Problem definition**

Multimedia proxies aim to reduce startup latency, network load and server load. An MoD proxy does this mainly by the means of caching. It may, in addition, perform other supplementary tasks to further reduce the network load. For example, it may transcode streams on the fly, translate the protocols used for transport and re-encode a stream to a different format.

As streaming media has relatively high resource demands, and when a proxy must serve many concurrent streams at different rates, a careful allocation of resources is needed to support such a load. The load on the proxy increases further, as transcoding, re-encoding and intelligent caching itself may be highly CPU intensive. We believe that by utilizing the capabilities of NICs with integrated, specialized NPUs we can offload the data-plane network processing to free resources on the proxy host. Further, we believe that an NPU can be efficient when processing the network traffic received at an MoD proxy. Two subjects draw our attention:

- 1. The caching strategies in multimedia take into account that the size of media objects tend to be too large to be cached in their entirety, unless they are extremely popular. The segments of media objects that are not cached must therefore be fetched from a server and then forwarded through the proxy. We specifically believe that the processing of this network traffic can be offloaded onto an NPU.

- 2. Network processing in a traditional proxy architecture is slow. *Operating Systems* (OS) provide generalized abstractions and security features, such as a network stack and memory protection boundaries. These features require many operations to be performed in order to process a network packet in the application layer. We believe that an NPU can be used to optimize the network processing needed in an MoD proxy.

To illustrate the feasibility and expediency of an offloaded proxy, we will in this thesis design and implement an MoD proxy prototype on a NIC with an Intel IXP1200 chip [Intel01b]. The implementation will basically consist of two parts, an RTSP proxy and an RTP forwarder. The RTP forwarder will be a proof-of-concept to show application layer forwarding of network traffic. At the same time, the prototype will be the basis of a framework for further work in the area.

# **1.3. Outline of document**

The rest of this document is divided into two parts; Part I, "Background" will describes the theoretical and technological foundation upon which this thesis is built. This is done in Chapter 2-4. Part II, "Design, implementation and evaluation" will describe the contributions made in this thesis in Chapter 5-7.

**Chapter 2**, *Distributed multimedia systems*. This chapter gives an overview of multimedia applications and essential background on distributed multimedia systems.

**Chapter 3**, *Proxies*. Here proxies are presented for distributed systems in general and for MoD systems in particular. The properties of an MoD architecture employing proxies are given and different system architectures are presented along with MoD caching strategies.

**Chapter 4**, *Network processors*. In this chapter a general introduction to NPUs are given before details about the IXP1200 and the Intel's IXA development platform are presented.

**Chapter 5**, *Design and implementation*. This chapter describes the design considerations and the implementation details of our prototype MoD proxy. It covers the components needed to realize an MoD proxy and the details of how the current implementation works.

**Chapter 6**, *Experiments, results and analysis.* In this chapter we will give a precise explanation of how we conducted our experiments and what results they produced. Then, the results and contributions are analyzed with respect to our goals and background material.

Chapter 7, *Conclusions and future work*. In the final chapter we summarize our work and describe in what areas we should focus future efforts.

# Part I. Background

### Chapter 2.

# **Distributed multimedia systems**

An image, a sound, they are one in the same, just one likes to move and one stays the same.

-Karate

Multimedia allows information to be presented in new ways. It has made its way into regular people's lives and is here to stay. Multimedia distribution across networks is however in its infancy. Several problems must be solved before high quality multimedia can be accessible in large scale packet switched networks. This chapter introduces multimedia. The subjects are: application characteristics, requirements, distribution and protocols.

# 2.1. General

Multimedia is, in simple terms, the combination of two or more media in relative synchronization. It enables human interaction and presentation of information. Any data consisting of a combination of text, sound, pictures, animation and video is often regarded as multimedia data. Synchronizing the media involves preserving their relationship in time. A movie combining the media of video and sound will synchronize the voices of the actors with their facial expressions. Even old silent movies combine two media, text and motion pictures, though in this case there is no synchronization.

A multimedia system is any combination of computer components that have the ability to present, create or deliver multimedia data. These components may be networks, operating systems and other software. It is the availability of resources in these components that determine the perceived quality of the multimedia. If one component fails to achieve the required performance, it becomes the *bottleneck* of the system, and no matter how well the other components perform, the end result is influenced by this component.

Film is just one real-life application. The range of common multimedia applications also includes video conferencing, gaming, learning software, and reference material such as encyclopedias.

## 2.1.1. Classification

The multimedia applications above may be classified using several different characteristics. Schemas are available that classify all applications or some subset of them. They are tools that ease the mapping of what requirements the application at hand has.

### **2.1.1.1.** Taxonomy of applications

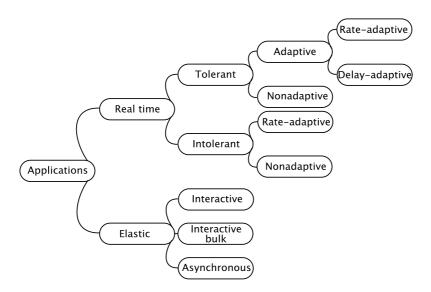

One classification schema, shown in Figure 2.1[Peterson00], regards all applications as either *elastic* or *real-time*.

The elastic classes of applications has no time bound for the delivery of data. They are however, usu-

ally not loss tolerant, i.e., they require reliable data transfer. Applications that fall into this category are typically text based chat, file transfers and email. These applications can further be classified as respectively interactive, interactive bulk and asynchronous. These applications do not depend on when the data arrives, as long as it arrives. They could benefit from timely delivery of data, but this is no requirement.

*Real-time* applications do, as opposed to elastic applications, require timely delivery of data. This means that if the data is not received within some time-frame, it is rendered less usable for the application, or not usable at all. For example, continuous media playback is affected by variations in delivery of data. A user will experience much of this jitter as low quality, due to skips in the playback. Other applications have heavier demands on timely delivery, such as industrial assembly lines with synchronization between robot arms. If a message arrives late to one of the robot arms the system will be out of sync.

Real-time applications can further be classified according to their loss tolerance. The assembly line application is an *intolerant* application as loss of data is unacceptable and would wreak havoc on the assembly line. The voice playback application however, allows occasional data loss, and is thus a *tolerant* application.

Another characteristic of real-time applications is their adaptive properties. The intolerant applications can adapt to the rate of data or not adapt at all. Tolerant applications on the other hand may, apart of being *non-adaptive*, adapt to both rate and delay. Video and sound playback may be adaptive applications. Voice is adaptive to changes in delay, i.e., *delay-adaptive*. This means that when playing back speech, the silence between words in a sentence can be shortened or lengthened to some extent, without being noticeable. Many audio encodings can also lower or vary the bit-rate of a recording or a stream by removing frequencies that cannot be heard. Video playback has the same characteristics as audio. The delay between frames can be varied, either by quickening the frame rate or slowing it down. There are also video encodings that can reduce the bit-rate by reducing the quality of each frame. Video and audio are therefore both *delay-adaptive* and *rate-adaptive*.

Figure 2.1. Taxonomy of applications

#### 2.1.1.2. Synchronicity

Distributed multimedia applications can, in addition to Peterson's taxonomy, be either synchronous or asynchronous<sup>1</sup>. The distinction is here how the two endpoints communicate. In synchronous communication both parties are using the application simultaneously. Though they may be separated in

<sup>1</sup>*The terms synchronous* and *asynchronous* are used in many research areas within computer science. Such as in programming, I/O systems and in communication.

space, they must both be present at the same time, e.g., in a video conference, when using VoIP or when participating in a real-time game. Asynchronous communication, on the other hand, is indirect and the parties may be separated in both time and space; it allows exchange of information, without the need for every involved user being present. The data is typically stored on a server so that the receiving part may fetch it at a later point in time, e.g., MoD.

#### 2.1.1.3. Interaction

Interaction is a characteristic that further differentiates multimedia applications. In reference material, such as Web pages, it is common to use hyper linking to navigate and switch between different media. Other means of interaction are possible, such as voice control and eye movement. In playback applications interaction, if present, involves navigating back and fourth, pause and stop. Such interactive features are called VCR operations. The number of interactive features, or the level of interaction separates these applications into different classes [Buddhikot98].

### 2.1.1.4. Classifying MoD

MoD applications, such as *News-on-Demand* (NoD), *Video-on-Demand* (VoD) and *Learning-on-Demand* (LoD), are a set of multimedia streaming applications. MoD is, with respect to the two classification schemes described, a real-time, tolerant, adaptive and asynchronous application. The user expects continuous playback of the media. This requires timely data delivery, which make MoD a real-time application. It is tolerant to the occasional loss of data, although playback quality will be reduced. Depending on the nature of the encoding, a media stream may also reduce the rate at which data is sent. This is rate-adaptive behavior. An MoD application is asynchronous due to the fact that the distributor may upload a media file to a server. This makes the media available for several users at any time.

The classification of a multimedia application will, among other things, dictate the requirements of how it is handled by a multimedia system.

# 2.2. Requirements

The classification of a multimedia application gives a high-level understanding of what is required by a multimedia system. As most multimedia applications are real time applications they have implicit demands of timely delivery. They usually allow some loss of data and have adaptive properties. If they have interactive characteristics, further demands are put on the system.

Nevertheless, compared to traditional textual data, the digitalized representation of video and sound require more storage space and bandwidth, due to higher data rates. This is because the information needed to encode light and sound waves in a rich way is a lot more than for example the eight bits usually needed to represent a common character. More bits are therefore required to store media files. This remains a fact even though compression is widely used. How many bytes it takes to store a media object depends on the desired quality, the chosen encoding algorithm and the playback length., e.g., see Example 2.1, Example 2.2 and Example 2.3.

#### Example 2.1. Audio data rate and disk usage

Audio in pulse code modulation coded *Compact Disk* (CD) quality uses 16 bit samples at 44.1 kHz with two stereo channels [Steinmetz95]. This gives a bandwidth requirement of 1.35 Mbps and a storage requirement of 607.50 MB for one hour of audio.

The bit-rate of media objects requires large disks, but it also requires that the communication system

is able to handle these rates. This includes every component that participate in the communication; the operating system, the entire network, every router and the server and client application.

#### Example 2.2. DVD data rate and disk usage

A Digital Versatile Disc (DVD) of the current standard, using the Moving Picture Expert Group (MPEG) codec version 2 has, for video, the maximum video bit rate of 9.8. The average video bit rate is about 3.5 Mbps, but this is dependent on length, quality, amount of audio, etc. After system overhead, the maximum rate of combined elementary streams (audio + video + sub picture) is 10.08 Mbps [Taylor04]. The size of a one hour long video is then 1.575 GB using average bit rate.

The continuous and real-time characteristics of films, speech, music and multimedia in general have other requirements besides storage space and bandwidth. The amount of delay and jitter must be kept as low as possible throughout the system. For example, if any component fails to process video or audio data in time, glitches in the presentation will be the result. The viewer might as a consequence give up or gradually lose interest. Further, if a video is to be experienced as flawless, there can be no more than  $\pm 80$  ms of skew in lip synchronization. Even higher demands on jitter occurrence are present when two stereo audio streams are played back. A person will detect  $\pm 11$  µs in this setting, so hardly any jitter at all will ruin the playback [Steinmetz95].

#### Example 2.3. DivX data rate and disk usage

DivX is a codec derived from the MPEG-4 standard. It has become a very popular codec for exchanging movies over the Internet [Zimmerman03]. DivX is able to reduce the size of an existing MPEG-2 encoded file 6.5 times, e.g., the required playback bandwidth drops from 5.6 Mbps to 870 Kbps. The disk usage is reduced from 423 MB to 63.8 MB. A one hour long video at 870 Kbps requires 393 MB worth of storage.

A real-time system guarantees that deadlines are met while playing back multimedia or other content with real-time requirements. Such systems guarantee QoS. QoS is an abstract term that can be used on many levels. In general, it can be defined in two parts:

- 1. A set of qualitative and/or quantitative attributes that specify the requirements of an application.

- 2. A mechanism that ensures that the specified requirements are met by a system running the application.

A user may typically specify a high abstraction of what quality he/she wishes to receive. For example, low, medium or high quality. On a lower level this specification is translated to a more fine-grained set of quantitative attributes, so the system may decide if it is able to meet the requirement or not, e.g., bandwidth, startup latency, jitter and correctness. In a real-time system, the system grants access and then ensures that the requirements are met, if it is able to satisfy them at the time. QoS is therefore also regarded as a contract between the user and the system. The user specifies what he or she wants, and the system provides it. However, real-time systems are rare, and no such support is available in the Internet, unless dedicated resources are set up. However a QoS agreement or contract needs not regard hard deadlines, or require reserved resources. A QoS contract may simply be that certain applications are prioritized. This basically means that throughout the system, applications are handled according to their priority. For example, events, actions and messages from a high prioritized applica-

tion will be handled by the system before those with a lower priority. Thus, the QoS contract is met if the priority scheme works. In the Internet this contract is *best-effort*, i.e., you get what is available, but without any guarantees.

Multimedia systems will need QoS mechanisms to fully support the requirements of multimedia applications. Since such support is inexistent in the core of packet switched networks, other measures have to be considered to improve a multimedia system's ability to provide satisfactory quality when streaming media.

To lower the bandwidth requirement in a system, the data-rate of video streams may be adapted. This further allows heterogeneous networks with different bandwidth capabilities to receive streams of different data-rates. When adapting to jitter, certain codeces, such as MPEG, allow for parts in the video to be discarded. Also, to reduce the effect of jitter, playback buffers are used at the client side so that jitter from the network is masked away. However, this fails if a packet arrives after the playback buffer is empty.

# 2.3. MoD access patterns

Requests for media objects tend to have certain characteristics. The frequency of access is said to follow the Zipf distribution [Sitaram00]. This means that only a few of the available objects are requested by the majority of the users. As a rule of thumb 10% of the objects are requested 90% of the time. Compared to other web content this is a clear characteristic of media object access, as web content of medium or low popularity usually include 50% of all material accessed [Wang99]. Newly published media objects tend to be the most popular objects, e.g., the top ten most popular videos in rental shops tend to be the newest ones. The access frequency of an object is often reduced over time.

When requested, media objects are usually consumed from start to end. If they are not fully consumed, they are usually canceled at an early stage [Acharya00]. Objects are seldomly accessed by the same person repeatedly.

The access to media objects tend to be "write-once-read-many", which means that the content rarely changes after being published. Users usually only have read-only interaction, much the same as a video player or music player.

The observed access patterns of media objects may be used to optimize the systems that deliver them. They also have an effect on what architectural choices that are made to build multimedia systems.

# **2.4. Distribution architectures**

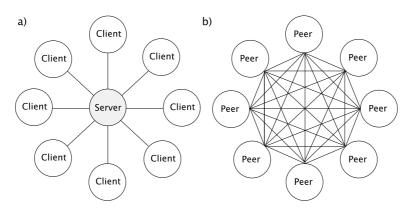

A distributed multimedia system can be built with a client, a network and a server [Sitaram00]. The architectural choices of a distributed architecture may have a large impact on how well the system works as there are different pros and cons associated with each architecture. There are three main distribution architectures; *hierarchical, distributed* and *hybrid* architectures.

The classic architecture is the hierarchical. It is called the *client-server* architecture and is shown in Figure 2.2 a). This is the model that traditionally has been used in the Internet. It is a simple scheme, where full control is held by the centralized server. The drawbacks of a pure client-server architecture is that the server represents a single point of failure. That is, if the server fails during execution the whole system breaks down. Another drawback is that the server is a potential bottleneck in the system, as all requests must be handled by it. If load exceeds the capacity of the server, then the rest of the system will suffer equally and the service will be degraded. Further, as the central server's geographical location potentially may be far away from the clients, the latency may be high. This will result in clients having to wait a long time before receiving any response from the server. Also, as long distances often imply that every packet must be routed through many nodes, each packet's total time in between the server and the client has a higher probability to vary (jitter).

The benefit of the client-server architectures is, as mentioned, that the server has control of the distribution of information to the clients. It is easy to administer such a scenario, both when publishing new content, charging for use and updating software. The main reason why it is so, is that data does not need to be replicated. Everything is centralized. Charging for services is easily managed by a centralized server and it is also simple to manage any state information as it needs not be replicated. Having a single copy of every accessible object also reduces the impact on the system when an object changes.

The opposite of the client-server model is a distributed architecture called the *peer-to-peer* model, see Figure 2.2 b). This is a collaborative model where every node is connected to every other node, and they all have the same amount of control, i.e., they are "peers". The P2P architecture has the advantage that it makes use of the resources that are available on the connected nodes. This distribution of computation removes the bottleneck represented by the server in a client-server architecture. The P2P architecture does not have a single point of failure, as every node has the same amount of control. If some nodes fail, the rest will still be able to function without them.

The P2P model is more complex than the client-server model, and no simple access control may be implemented as control is shared by all nodes. This makes charging for the use of services harder. Resources will typically be replicated across several nodes for reliability, making consistent updates of changes harder. Another issue with the complexity of P2P architectures is the need for a substantial amount of communication control messages between the peers. These messages are used to exchange synchronization and meta data. This may flood the network and lead to scalability problems.

The *hybrid* architecture is literally a hybrid of the hierarchical, i.e., client-sever and the distributed model, i.e., the P2P model. It incorporates characteristics from both, by for instance having a centralized meta-data server, while storage is distributed. Many variations can be implemented and these architectures may remove some of the drawbacks while keeping most benefits of an architecture.

Existing video and audio streaming solutions tend to choose the client-server architecture<sup>2</sup>. The client-server architecture has also been the preferred architecture for commercial game vendors because of the benefits described above, but it is suggested that a hybrid architecture might be better suited [Mauve02], while still preserving the needs of commercial vendors.

**Figure 2.2. Distribution architectures**

Regardless of the distribution architecture, there are more ways of distributing the packets that flow from a server or in between peers. In the Internet there are three ways to do this. Packets may be sent to everybody with *broadcast*, to a set or a group with *multicast* or to one receiver with *unicast*.

Television uses broadcasting networks to distribute their media. This means that everyone that listens on a certain channel, will receive what is on at that particular moment. MoD, however, must be able to serve a client whenever it requests to view a certain media object. Therefore, broadcasting is a less suitable distribution mechanism. Many variations of broadcasting have been created to adapt to an <sup>2</sup>Streaming solutions such as the Darwin Streaming Server [Apple04], Helix DNA Server [Real04a] and KOMSSYS [Griwodz03] all use a hierarchical architecture.

MoD scenario, but have been unable to provide *true-MoD*, i.e., that a user can request a media object at any time.

Most applications in the Internet usually use *unicast* communication. This means that there is only one source and one destination participating in the data transfer. If there are more than one receiver, one copy must be sent to each of them. This is a scalability problem as each unique packet sent to the network must be copied to a multiple number of receivers.

To solve this *multicast* was purposed. Multicast may also be called group-cast, as clients must join a group in order to receive the information that is sent out. In contrary to unicast, only one packet is sent out from a sender and it propagates the network as one copy. Along the network path, the packets will be duplicated if there are clients that have joined from different directions. While multicast is supported by the IP, it is usually blocked by *Internet Service Providers* (ISPs). This may be because multicast makes it hard to account for network usage and it is vulnerable to *Distributed Denial of Service* (DDoS) attacks.

# **2.5. Protocol overview**

Protocols define the format and order of messages exchanged between two or more communicating entities, as well as actions taken on the transmission and reception of messages or other events [Kurose04]. A multimedia streaming system makes extensive use of protocols. Protocols are needed to control interaction, setup and transfer the data. Protocols also exist to retrieve metadata about streaming sessions, e.g., the *Session Description Protocol* (SDP) [Handley98].

Figure 2.3 shows the *Open Systems Interconnect* (OSI) model alongside the Internet TCP/IP protocol stack [Socolofsky91]. Multimedia applications may employ the whole range of protocols, depending on the characteristics of the application.

The protocol pair that is commonly used for streaming is the combination of the *Real Time Streaming Protocol* (RTSP) [Schulzrinne98] and the *Real-time Protocol* (RTP) [Schulzrinne96]. Both these are standards defined by IETF and are widely supported by streaming solutions. In this section, we describe those that are relevant for this thesis.

| 7 | Application  |             |

|---|--------------|-------------|

| 6 | Presentation |             |

| 5 | Session      | Application |

| 4 | Transport    | TCP/UDP     |

| 3 | Network      | IP          |

| 2 | Data Link    | Data Link   |

| 1 | Physical     | Physical    |

|   | OSI          | TCP/IP      |

Figure 2.3. The OSI stack and the Internet protocol stack

### 2.5.1. Real Time Streaming Protocol

RTSP [Schulzrinne98] is an application-level control protocol for streaming. It resembles and has overlapping features with the *Hypertext Transfer Protocol* (HTTP) version 1.1 [Fielding99].

The main purpose of RTSP is to establish and control streams of continuous media. Usually, the actual data-transfer is performed out-of-band using RTP, but RTSP is not bound to any specific transport protocol. Data may even be interleaved within RTSP messages. To control a session, RTSP maintains session state for each stream.

RTSP supports both multicast and unicast streaming. This may be both playback or recording of such, but the standard does not require an implementation to support recording.

To establish and control streams several methods are defined in the standard. Those *required* (OPTIONS, SETUP, PLAY and TEARDOWN) by an implementation are shown in Example 2.4.

Other methods are defined as well, such as DESCRIBE, PAUSE, ANNOUNCE, GET\_PARAMETER, RECORD, REDIRECT and SET\_PARAMETER. Not all of these methods change the state of a RTSP session, only SETUP, PLAY, RECORD, PAUSE and TEARDOWN do. SETUP starts a session and allocates resources for a stream. PLAY and RECORD start data transmission on a stream that has been set up. PAUSE temporarily halts a stream without releasing its resources. Finally, TEARDOWN will halt the stream and free the resources allocated by the session.

The first thing that happens when a client initiates a session, is that it sends a SETUP request to the server. The central part of this request is the transport specification. In Example 2.4, the client tells the server that it wants to use RTP unicast to transport the data out of band on port 1004. The stream could also be sent over TCP, interleaved in RTSP messages or to a multicast group. The server replies with a status message verifying the request of the client. It also adds the server port pair, where it enables data to be received. Note that the first number in the client and the server port pair is for data retrieval and the second is for any control data on the stream. The data port always is even, and that the control port is always odd, and one higher than the data port. The server has now set up a session on its side and the session number can be used to identify subsequent RTSP requests. The PLAY request from the client therefore adds this number to the session header. The client wants to play the whole length of the stream, so it sends a range header indicating this. The server sends a status message, and the streaming starts on the channel setup by the transport specification. When the object is played back, the client sends a TEARDOWN request and the session is removed.

#### **Example 2.4. Basic RTSP session**

| C->S | <pre>SETUP rtsp://10.0.0.2:554/ex.mpeg RTSP/1.0 CSeq: 1 Transport: RTP/AVP;unicast;client_port=1004-1005</pre>                   |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| S->C | <pre>RTSP/1.0 200 OK<br/>CSeq: 1<br/>Session: 8<br/>Transport: RTP/AVP;unicast;client_port=1004-1005;server_port=1008-1009</pre> |

| C->S | PLAY rtsp://10.0.0.2:554/ex.mpeg RTSP/1.0<br>CSeq: 2<br>Session: 8<br>Range: npt=0-                                              |

| S->C | RTSP/1.0 200 OK<br>CSeq: 2<br>Session: 8<br>Date: 25 Feb 2004 18:07:02 GMT                                                       |

| C->S | TEARDOWN rtsp://10.0.0.2:554/ex.mpeg RTSP/1.0<br>CSeq: 3<br>Session: 8                                                           |

| S->C | RTSP/1.0 200 OK<br>CSeq: 3                                                                                                       |

## **2.5.2. Real-Time Transport Protocol**

RTP [Schulzrinne96] is the Internet-standard protocol for the transport of real-time data, including audio and video. It can be used for media-on-demand as well as interactive services such as Internet telephony, real-time control and distributed simulation. RTP consists of a data part and a control part. The latter is called the *RTP Control Protocol* (RTCP).

The data part of RTP is a thin protocol providing support for applications with real-time properties such as continuous media, e.g., audio and video, including timing reconstruction, loss detection, security and content identification. It also features negotiation of what encoding to use.

RTCP provides support for real-time conferencing of groups of any size within the Internet. This support includes source identification and support for gateways like audio and video bridges as well as multicast-to-unicast translators. It offers QoS feedback from receivers to the multicast group as well as support for the synchronization of different media streams.

While UDP/IP is RTPs initial target networking environment, efforts have been made to make RTP transport-independent so that it could be used, say, over TCP, Novells IPX protocol or other protocols. RTP does not address the issue of resource reservation or QoS control; instead, it relies on resource reservation protocols such as RSVP.

## 2.5.3. Session Description Protocol

SDP describes multimedia sessions for the purpose of session announcement, session invitation and other forms of multimedia session initiation.

Session directories assist the advertisement of conference sessions and communicate the relevant conference setup information to prospective participants. SDP is designed to convey such information to recipients. SDP is purely a format for session description - it does not incorporate a transport protocol, and is intended to use different transport protocols as appropriate. Example transport protocols for SDP include the *Session Announcement Protocol* (SAP), *Session Initiation Protocol* (SIP), RTSP, electronic mail using the MIME extensions, and HTTP.

SDP is intended to be general purpose so that it can be used for other network environments and applications than just multicast session directories. However, it is not intended to support negotiation of session content or media encodings.

The SDP communicates the existence of a session and conveys sufficient information to enable participation in the session. In this thesis we omit the use of this protocol when implementing RTSP. The session information is fetched manually.

# 2.6. Summary & challenges

When running distributed multimedia applications in the Internet, the main problem is getting time sensitive data to its destination in the appropriate period of time. The challenges are especially demanding on the server-side and in the network. Streamed data needs a relatively continuous flow of information in order to maintain its integrity. There is no support for this in IP networks, without dedicating a route for a particular stream.

IP networks work well for streaming if every packet spends the same amount of time reaching their fellow destination. However, this only applies in a perfect network where no congestion occurs at any routers and where all packets follow the same route or a different route with the same latency. Congestion is a result of buffering within the router. The router must buffer packets if the capacity of one output is exceeded, i.e., too many of the incoming packets are destined to the same output port or if it experiences bursts on input ports. Packets must therefore wait in the buffer or they are dropped because the buffer fills up. Packets may also take different routes through IP networks, as routers may appear or disappear. Combining congestion with alternative routes results in packets arriving at their

destination out of order and the time it takes them to reach the destination may vary.

Another challenge is the latency itself. Synchronous streams in opposite directions, e.g., live conversation, must be transmitted through the net before the receiving side can reply. This will, if the latency is high, result in long gaps from when you end a sentence until you receive a reply. Also in asynchronous streaming, e.g., MoD, a client might have to wait quite a bit before the stream can start playback. This start-up delay is further lengthened if the client has to buffer data to alleviate jitter in the network.

Multimedia applications may also occupy a lot of bandwidth. The high bit-rate puts load on the network and makes multimedia servers highly I/O centric. On the server-side this represents a scalability problem as resources are bound to one stream for a long period of time.

In the next chapter, we describe a pragmatic solution suggested to improve this situation: the proxy.

### Chapter 3.

# **Proxies**

Every peer... may make another lord of parliament his proxy, to vote for him in his absence.

-Blackstone

Proxies are network nodes in the vicinity of clients, performing tasks on behalf of a server. They traditionally perform caching, to reduce latency for clients, reduce network load and offload servers. These nodes also have other uses depending on the context in which they run. For instance in an MoD setting, they may perform re-encoding, encryption and adaption of multimedia streams. They may also have general features such as access control, re-routing and simple QOS mechanisms.

# 3.1. General

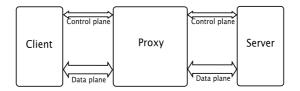

A proxy is someone that acts on the behalf of others. In politics, a proxy can be given the authority to vote on the behalf of someone else. In computer science, the proxy may be a process or an object acting on behalf of a server process or a remote object<sup>3</sup>. Whether the proxy runs as a stand-alone process on a separate host or is embedded in a local process running on the client host, it is located closer to the client, along the network path, compared to the server process or remote object. This is shown in Figure 3.1. Every remote call the client makes is intercepted by the proxy so that certain operations can be performed. These operations vary as to which context the proxy runs in.

Figure 3.1. Basic proxy architecture

<sup>&</sup>lt;sup>3</sup>To be precise, the role of a proxy is twofold. It may retrieve information on behalf of a client or deliver information on behalf of a server.

Proxies<sup>4</sup> were first introduced as a way for machines behind firewalls to access web content [Wang99]. This was achieved by placing a host machine on the outer rim of the network with access to the Internet. The observation was made that the users within such firewalled corporate networks would access much of the same content. By having the proxies cache text and images, the users would get faster access to it. The central server running the service would not have to process these requests and fewer packets would be sent to the outside. Today, it is fairly common for *Internet Service Provider* (ISP) and *Local Area Network* (LAN) administrators to deploy proxies to ensure quick response when users load web content, by caching images and text. In HTTP, a client may be configured to send every request via a proxy towards the server. The main purpose of the proxy is then basically to cache any content the client may want to receive and only re-retrieve it if it has been altered on the server. The proxy will then be able to serve the cached content on behalf of the server. If additional content is wanted, it will forward such requests to the server, and cache the response before sending it back to the client. An HTTP proxy may also log web activity and block certain content if so desired. The HTTP contains specific fields concerning proxy operations, such as forcing reload or specifying that the content cannot be cached due to dynamically changing content.

In MoD, proxies are used in the same way as in web caching. However, larger objects, different access patterns and application requirements are characteristics that must be considered. These characteristics are explained in Section 3.2.

Proxies are also present in distributed gaming research. A Generic Proxy System for Networked Games [Mauve02], suggests that a number of interconnected proxies be deployed at the edge of the network to help minimize the drawbacks, but also keep the benefits of a client-server architecture. The proxies may then perform various actions on behalf of the server and also send messages among themselves in order to relieve the server.

Another suggestion for distributed games [Bauer02] is to use network aware *booster boxes*. "Booster boxes acquire network awareness by monitoring traffic, measuring network parameters such as delay, by participating in routing exchanges, or by acting as an application-layer proxy server. Each booster box serves a number of clients in its network vicinity and performs caching, filtering, forwarding and redirecting of game events in a game-specific way."

# **3.2. MoD proxy caches**

As with HTTP proxies, the MoD proxy's prime operation is to cache objects. However, other application specific considerations will have to be made in MoD proxy caches than in HTTP proxy implementations. The prime difference is how objects are cached and how they are replaced. MoD proxies have other application specific uses besides caching. They may perform dynamic transcoding, i.e., change the bit-rate at which a stream is sent. They may also support changing the encoding on the fly as well as transport protocol translation, i.e., using UDP in a Wide-area network and TCP in a access network [Griwodz04]. It is therefore hard to use one single proxy implementation to handle both classic web objects and media objects.

Two primary observations motivate the caching of media files in an MoD system. First, an application needs to play back large amounts of data with timely delivery. The continuous media makes the application sensitive to jitter. To reduce this, the client usually buffers a certain amount of data before starting playback. This means that media playback cannot be started until this buffer is filled up. As mentioned in Section 2.4, the distance from client to server also is a variable that regulates latency. A proxy cache can alleviate this startup-latency by being deployed in the vicinity of the client. Media files also consume a lot of bandwidth due to their high bit-rate. An early cache hit would therefore reduce the load on the core of the network.

<sup>&</sup>lt;sup>4</sup>Proxies are also used in *Remote Procedure Calls* (RPC) and *Inter Process Communication* (IPC) though the operations performed differs from those in a HTTP proxy. In IPC, the operations mainly consist of marshalling and UN-marshaling the messages that are sent to and received from the network. Proxies are sometimes called stubs in these contexts.

Secondly, media objects in MoD seldom change, and the "write-once-read-many" pattern is a strong argument for caching these objects in contrast to regular web-objects. There is therefore a low administrative overhead to keep caches up to date. The main problem when caching media files is the storage requirement, see Example 2.2. It is impossible to cache the immense amounts data that a collection of media files represent entirely in the memory of a host. It is even hard to cache all available media objects on disk. The Zipf distribution [Sitaram00], however, indicates that a good cache hit prognosis is to cache the 10% most popular films. The hard part is then to know what films are the most popular. Many caching strategies exist to deal with the problem of huge media objects. The solution is to partition an object and only cache parts of it. Examples of such algorithms follow in Section 3.2.2.

An MoD system must support the heterogeneity in the Internet. Proxies have to accommodate the requirements of different clients with respect to streaming rates and encoding formats. In commercial streaming systems, this has been solved by replicating objects at different rates and formats. This approach has prohibitively high demands on storage and bandwidth. To avoid this, proxies may perform on-demand transcoding of the streams. The intensive computation overhead of transcoding however prevents a proxy from supporting a large client population [Liu03].

Bommaiah et al [Bommaiah00] design and implement a proxy using the Internet-standard protocols RTSP and RTP. They use their prototype to show the performance gains by inserting proxies in a streaming environment. Their results, using a single proxy, show that by caching the 50 first seconds of a 1 minute media object, they are able to reduce network and server loads by 75%. They also show a 50% improvement in startup latency, by streaming the first three seconds ten times faster than the streaming rate.

Another proxy scheme presented by Acharya and Smith [Acharya00], called MiddleMan looked at the caching of movies within a campus LAN. While having proxies cooperate when caching objects, they achieved a high aggregate storage space. Their proxies cooperate through a coordinator process that held information about where elements were located. They found that the effective bandwidth of their entire streaming system increased by a factor between three and ten.

## **3.2.1.** Properties

To serve their purpose, proxy cache systems should fulfill certain qualities. A number of these are discussed for Web caching[Wang99] and include fast access, robustness, transparency, scalability, efficiency, adaptability, stability, load balancing, dealing with heterogeneity and simplicity. These properties also, as described below, apply to MoD proxy cache system.

- *Responsiveness*: Users expect applications to respond quickly to commands. If not, they would grow inpatient and maybe stop using the application. This property is important in an MoD cache. In a distributed system without real-time support, a multimedia player uses jitter avoidance buffering to "ensure" continuous playback. The startup latency will therefore to a higher extent be noticeable to a user compared to streaming a text document. So, a replica of the data with shorter transfer time to the client, would increase the responsiveness of the application, in respect to both startup latency and interaction latency.

- *Robustness*: How robust a caching system is to failures is a property that for a user is experienced as availability of the service. Having a single point of failure in an MoD caching schema should be avoided. If one proxy crashes, the system should not be rendered inaccessible to clients. The system should provide fallback mechanisms if one or a few nodes fall out. Proxies may form an overlay network by being connected to each other in order to provide such robustness.

- *Transparency*<sup>5</sup>: A system should appear as a whole and conceal details of the underlying components from the user. This would imply that inserting a cache in the network should not have implications for the user, other than the improvements of the service. The user should not need to be aware of whether the content is coming from the server or the proxy, nor of how the possible per-

<sup>&</sup>lt;sup>5</sup>There are several categories of transparency such as, access, location, concurrency, replication, failure, mobility, performance - and scaling transparency [Coulouris01].

formance gain is achieved.

- *Scalability*: Scalability is how well a solution to some problem will work when the size of the problem increases. In a server or proxy system, the increase of resources used should be constant to the increase in usage. A caching scheme must therefore not impose heavy resource demands due to changes in density, usage or size of a network. Inserting proxies in a system should not increase resource demands. This means that any inter-cache protocols should be lightweight and not add numerous packets in the network. Also, every proxy must carefully allocate its resources so it may serve many clients without degrading its performance.

- *Efficiency*: The efficiency of a system is dependent on the throughput of it. The time spent by processing or communicating in an MoD caching system should therefore impose a minimal addition to delay on a stream. MoD cache should process as close to link speeds as possible and send few control packets into the net to achieve this. This is closely related to scalability.

- *Adaptability*: Environmental changes often mean that behavior must be altered as well. A cache should be able to adapt to changes in access patterns and proxy placement. It should either be aware of architectural changes or be configurable to adapt to such changes. It should also be able to adapt to changes in network load, by altering the data-rate in an MoD stream.

- *Load Balancing*: This property means to distribute the computation and network load. A caching scheme should avoid hot-spotting certain parts of a system. It should have mechanisms to distribute load on the network as well as the server.

- *Heterogeneity*: The Internet is built up using a collection of different computer and network technologies. This heterogeneity is challenging in many areas, and must be considered when designing distributed systems. A caching scheme must be able to handle the differences in the link -and network layers. MoD caches must in particular be able to deal with different formats for representing media. Such formats are MPEG-2, AVI, WMA, etc. Also an MoD proxy should be able to deliver different quality streams depending on the clients requirements.

- *Simplicity*: Keeping the scheme simple is important in order to easily implement and deploy it in an already existing system.

These properties have implications on the design of a proxy system because they dictate the goals of such a design. If a design holds efficiency as a prime concern, then adaption and transparency may get a lower priority. However, efficiency may also imply that the system should be simplistic. Whether the properties converge or diverge they impose tradeoffs in a design. There are other possible properties in such a system as well, security being one and extendibility another. These properties are often in conflict with scalability and efficiency, as they require resources and time consuming processing.

The properties above applies both to the internals of a proxy host and the surrounding system. The considerations are different if the proxy must cooperate with other proxies than if it is a stand-alone proxy. A design should not restrict itself, but allow extension so that the adaptability of the proxy to the surroundings can be met.

## **3.2.2. Caching strategies**

A well known fact is that the optimal way to perform caching is to always have the object that will be accessed next ready in the cache. Also, when the cache is full, the objects best to replace are the ones that will not be accessed for the longest time. If a caching scheme could predict this perfectly a perfect cache hit rate would be achieved. However, predicting the future is as impossible in computer science as in life. Caching algorithms try their best to predict what to place in the cache and what to replace when needed, based on typical application access patterns. In MoD, there are numerous such algorithms. Liu and Xu [Liu03] divide them into four categories for homogeneous clients, i.e., for clients that have identical requirements on data-rate, etc.:

- *Sliding-interval caching* caches a sliding interval of a media object to exploit sequential access of streaming media. If two consecutive requests for the same object occurs, the first will fetch the object from the server and incrementally store it in the cache of the proxy. The second request may then access the cached portion and release it when fetched. If several requests for the same object arrive close in time, the last request will be the one releasing the object from the cache. This algorithm can be very effective in saving network bandwidth and start-up latency when subsequent requests for the same object happen within close time intervals.

- *Prefix caching* caches the start of an object, called the prefix [Sen99]. When serving a request the proxy immediately deliverers the prefix to the client and, meanwhile, fetches the rest of the object, called the *suffix* from the server. When using prefix caching the size of the prefix is chosen based on available resources and optimization objectives. It can significantly reduce the start-up latency of a stream, but it does not reduce the network load or server load to the same extent.

- Segment caching is a generalization of prefix-caching. It partitions a media object into a series of segments and set different caching values on each segment. Usually, the first few segments are viewed as more important than those at the end, as they may be pre-fetched. However, if the media object is popular enough, it should also be possible to cache the later segments in a stream. If the popularity of an object decreases the proxy may discard large chunks of the object, but it has the possibility of leaving the first segments, e.g., the prefix of the object. This algorithm has about the same savings on start-up latency and network load as prefix caching.

- *Rate-split caching* partitions the data horizontally along the rate axis, instead of vertically along the time axis as the previous three algorithms do. The upper part of the data is cached in the proxy. This algorithm is attractive when the data is variable-bit-rate media. In a non-QoS network it improves the network load and start-up latency moderately.

The above strategies all implicitly expects the remaining non-cached data to be fetched from the server in order to satisfy homogeneous clients. However, to serve heterogeneity, layered caching is suggested. This method of caching requires a layered encoding of the data, i.e., the data is split into several layers: the most significant layer, called the *base layer*, contains data representing the most important features of the object, while additional layers, called *enhancement layers*, contain data that refine quality. The higher the layer is from the base, the more fine grained is the quality. Layered caching usually caches the lower layers, as they are relevant to all clients requesting the object. On cache replacement a layer is identified based on popularity, and its cached segments are removed from the tail until sufficient space is obtained.

A proxy cache also needs a strategy for replacing objects when the cache fills up. Several methods exist to do this. Podlipnig and Böszörmenyi [Podlipnig03] give a survey of such strategies. They classify them as follows:

- Recency-based strategies: These strategies take into account how much time has passed since the object was last referenced. These strategies are usually variants of the *Last Recently Used* (LRU) strategy, which simply replaces the object that has been in the cache the longest without any accesses.

- Frequency-based strategies: These strategies take into account how often a object is accessed, i.e., the frequency of references decides what to remove. These strategies are usually extensions to the *Least Frequently Used* (LFU) strategy. Objects that are seldomly accessed are removed.

- Recency/frequency-based strategies: These strategies combine recency and frequency factors to make caching decisions.

- Function-based strategies: These strategies use a function to calculate the value of an object. They use different weighting factors in the functions to calculate an appropriate value, e.g., age, size, cost of fetching the object, etc.

• Randomized strategies: These strategies decides what to replace in a randomized way.

In multimedia caching, the access patterns are a vital piece of information in order to make caching decisions. A movie that is accessed often can be regarded as popular and should probably remain in a cache. The *Eternal history, Conditional replacement and Temporal gap size* (ECT) [Griwodz00], is loosely based on the LFU strategy<sup>6</sup>. It accounts for all requests to an element, and stores this information in an eight entry history per element. Each entry in the history is the gap in time between two consecutive hits on a stored element. The ECT strategy does not remove the history of an element after it is removed, so elements have an eternal history. It is conditional as all first time elements are cached, but after being removed the history of the element will still exist and is used for future cache decisions. This strategy shows good simulation results when caching media objects in a large population system with many movies.

# **3.3.** Cache architectures

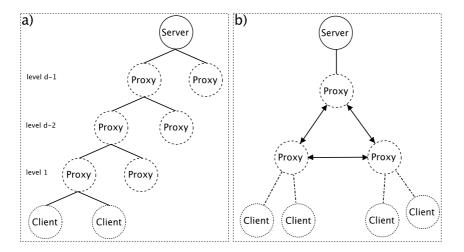

As shown in Figure 3.1 the proxy is an hierarchical extension to the client-server architecture. To realize many of the properties in Section 3.2.1, proxy designs usually include the possibility for proxies to interconnect. When a number of caches are inserted into a network, the probability of an object already being cached increases, i.e., a increased hit-probability [Acharya00]. What differentiates the available architectures is how information is exchanged between the nodes and how they are laid out in the network.

A *Hierarchical architecture*, as shown in Figure 3.2 a), divides caching in levels. A request will traverse up the hierarchy until the requested content is found, the response will then traverse back down the hierarchy, leaving a copy of the content at each subsequent level along the path. The drawbacks of this architectural scheme its that many replicas of objects are left down through the hierarchy. Also the high level caches become key access points that might go down or become bottlenecks. Lastly, a negative effect is that processing delay is added at each level of the hierarchy.

*Distributed architectures* or cooperative caching, as shown in Figure 3.2 b), only operate with one level of caches. Theses caches distribute meta-information on where to fetch cache misses. The distribution of the meta-information may be hierarchical, but fetching a cached object is only done within the same level. This model may experience high connection times and high bandwidth usage when used in large scale. Also, as with P2P, administrative issues exist.

Figure 3.2. Cache architecture

<sup>&</sup>lt;sup>6</sup>In the reference it says that ECT is based on the *Inter-Reference Gap* (IRG) algorithm, but personal correspondence with the author suggests that this is wrong.

The *Hybrid* proxy architecture is not shown in the figure, but it incorporates features from both the hierarchical architecture and the distributed architecture. A hybrid have caches cooperating on the same level, or in between levels. The requested cached object is fetched from the parent of neighboring cache with the lowest *round trip time* (RTT).

## 3.4. Data flow

The flow of packets in a proxy can typically be divided into a control-plane and a data-plane. In HT-TP proxies, this distinction is not as clear as in MoD proxies. The HTTP messages hold both control data and content, while for instance, using RTSP and RTP separates the two<sup>7</sup>. When not interleaving data, RTSP messages follow the control-plane and RTP packets flow in the data-plane. The separation of the two planes is shown in Figure 3.3. Both the data-plane and the control-plane are bidirectional. The control-plane experiences traffic in both directions during a RTSP session, but in the data-plane, traffic only flows in one direction, either from client to server or from server to client. The recording feature of RTSP is an example of what enables data to flow from client to server.

Figure 3.3. Proxy data flow

On a high-level, a proxy cache could be implemented as a process, or a set of communicating processes, running on a machine within the network. If one assumes that it is one process, this would act as both server and client. The server part of the process would handle incoming requests and serve these if able. If it is unable to respond to a request immediately, it would use the client-side of the proxy and connect to another proxy or directly to a server. When the requested object is found through the control-plane it would be transfered back to the proxy through the data-plane. The proxy would receive the object, cache it and send it further down the request path. As seen in Figure 3.3 the control-plane is assumed to be a lot thinner than the data-plane. This illustrates that the requests to establish a stream do not take up as much resources as the actual streaming.

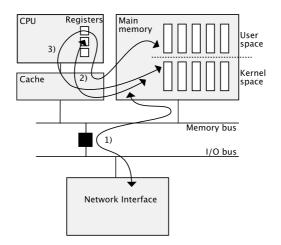

The internals of a proxy cache depend on what platform it runs on and how it is implemented. However, it would normally use a socket interface to communicate with the network. Every incoming packet on a network interface would find its way to the correct socket. Whenever a packet is received on the network interface card, it will emit an interrupt. This interrupt will normally activate the interrupt handler within the *Operating System* (OS) kernel. This results in a change of context in order to process the packet. The payload of the packet will then be transferred into kernel memory and will traverse up the network stack. Whenever application level data is received, the data must be copied to the memory of the user space application. Then, the proxy may deal with this data according to any application level protocol, like saving the data to disk, before any response is sent down the stack and transmitted by the NIC.

<sup>7</sup>Although RTSP allows for interleaving the data-plane, this is usually only done when circumventing firewalls.

Figure 3.4. Proxy data-path

The data-flow is illustrated in Figure 3.4. An interrupt and a bus transfer (1) is needed to get the packet into kernel memory. While being processed by the network stack, elements in memory will pass through the cache and the CPU registers (2). Then, when reaching the application, the packet payload must be copied to user space memory, and every memory element will be moved by the CPU to the user space memory location (3). If the application then needs to write data to disk, or send new data back out, additional copying and CPU processing is needed.

## 3.4.1. Copy operations

As explained above, every incoming payload of a packet must be copied to the applications memory location in user-space through the CPU. Several experiments show that copy operations represents a major bottleneck in high throughput systems, such as a multimedia server, or proxy. For example in [Halvorsen01] a series of experiments using different copy operations on a NetBSD platform, are described. When copying data into user-space using the *copyout()* function a 1024 byte block of memory was copied in an average of 0.48  $\mu$ s, i.e., about 447 cycles with interrupts turned off. Similar overhead is shown when copying from user space to kernel memory and also internal copying within kernel memory, regardless of whether interrupts were turned on or off. These tests were performed using an Intel Pentium II Xeon 933 MHz processor with a 256 PC800 RDRAM chip.

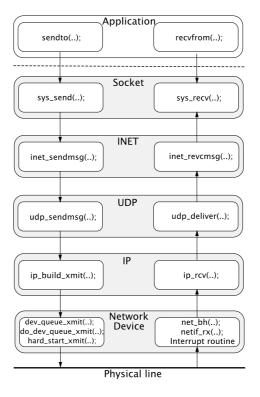

## 3.4.2. The Linux network stack